# 82C733 Universal Peripheral Controller IV

# Floppy Disk Controller

- Single-chip floppy solution

- Software compatible with NEC 765B and Intel 82077

- Perpendicular recording support

- 48mA disk drivers and Schmitt-trigger inputs

- Direct support for two drives, and up to four drives with external decoder

- Enhanced digital data separator

- No external filter components required

- Support for 250KB/s, 300KB/s, 500KB/s and 1MB/sec data rates

- Primary and secondary floppy address port selects

# **Serial Ports**

- Two NS16550 compatible UARTs

- 16-byte FIFO

- Modem control circuitry

#### IDE Interface

- Provides a complete IDE interface for embedded hard disk drives.

- Primary and secondary IDE address port selects.

### **Parallel Port**

- Compatible with IBM PC, XT, AT, and PS/2 architectures

- Standard and bidirectional parallel port

- 24mA parallel port output drivers

#### General

- Pin and Software Compatible with 82C735 without Printgine

- 100-percent compatible with IBM PC, XT and AT architectures

- 24mA AT/XT bus interface buffers

- Game port chip select logic

- On-chip power management features, controllable through hardware and/or software

- Configuration via software

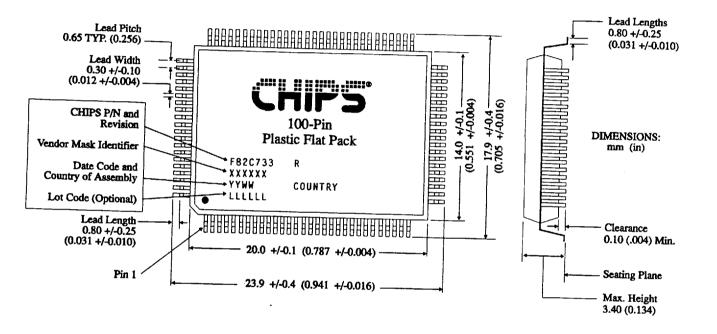

- 100-pin QFP package

Revision 1.0

Preliminary 82C733

# **Revision History**

| Revision | Date  | By | Comment                       |

|----------|-------|----|-------------------------------|

| 0.1      | 10/93 | PK | First Draft - Internal Review |

| 1.0      | 11/93 | PK | Initial Release               |

# **Table of Contents**

| Section                                | <u>Page</u> | <u>Section</u>                       | Page |

|----------------------------------------|-------------|--------------------------------------|------|

| Introduction                           | 7           | Floppy Drive Control (FDC) Registers | 55   |

| 4MB Floppy Disk Controller             | 7           | Digital Output Register              | 56   |

| Digital Data Separator                 | 7           | Tape Drive Register                  | 57   |

| NS16550 UARTs, IDE & Parallel Port     | 7           | Data Rate Select Register            | 58   |

| Power Management                       | 7           | Main Status Register                 |      |

|                                        |             | Data Register (FIFO)                 |      |

| Pinout Diagram                         |             | Digital Input Register               |      |

| Pin List                               | 10          | Configuration Control Register       | 61   |

| Pin Descriptions                       | 11          | Status Register 0 (ST0)              | 62   |

|                                        |             | Status Register 1 (ST1)              |      |

| Register Summary                       | 19          | Status Register 2 (ST2)              |      |

| Registers                              | 21          | Status Register 3 (ST3)              |      |

| Configuration Registers                | 23          | FDC Command Handling                 | 65   |

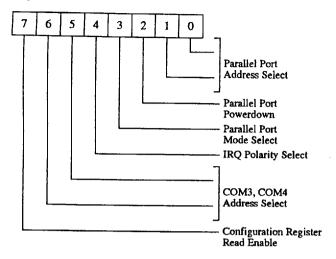

| Register CR00H                         | 24          | Command Phase                        |      |

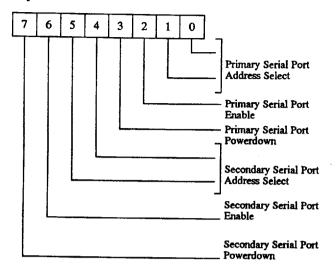

| Register CR01H                         | 25          | Execution Phase                      |      |

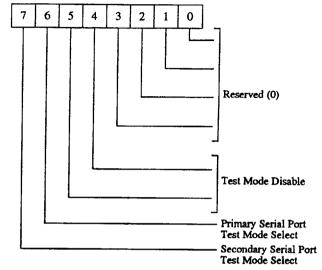

| Register CR02H                         | 26          | Non-DMA Transfers From FIFO to Host  | 65   |

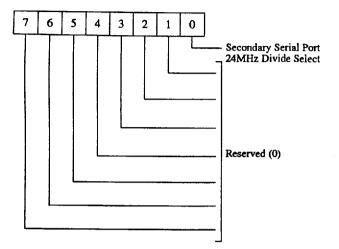

| Register CR03H                         | 26          | Non-DMA Transfers From Host to FIFO  | 66   |

| Register CR04H                         | 27          | DMA Transfers From FIFO to Host      |      |

| Register CR05H                         | 27          | DMA Transfers From Host to FIFO      | 66   |

| Register CR06H                         | 20          | DMA Transfer Termination             | 66   |

| Configuration Procedures               | 20<br>20    | Result Phase                         | 66   |

| Serial Port Registers                  |             | FDC Command Set                      | 67   |

|                                        |             | Command Summary                      | 67   |

| Receive and Transmit Buffer Registers  |             | CONFIGURE Command                    | 69   |

| Interrupt Enable Register              |             | DUMPREG Command                      |      |

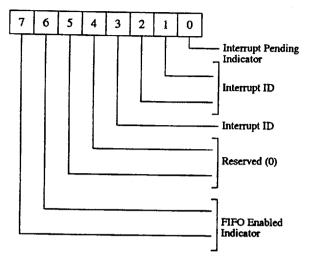

| Interrupt Identification Register      | 34          | FORMAT TRACK Command                 |      |

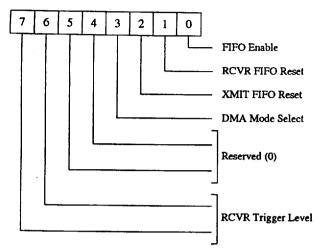

| FIFO Control Register                  | 33          | INVALID Command                      |      |

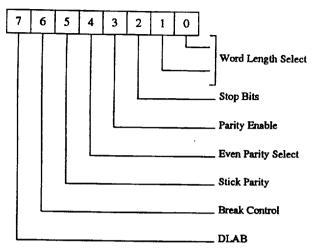

| Line Control Register                  |             | LOCK Command                         |      |

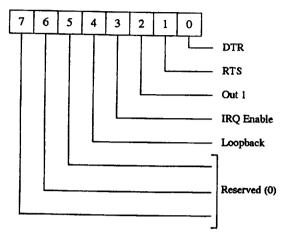

| Modern Control Register                | 38          | PERPENDICULAR MODE Command           |      |

| Line Status Register                   |             | READ DATA Command                    |      |

| Modern Status Register                 | 40          | READ DELETED DATA Command            |      |

| Scratchpad Register                    | 40<br>41    | READ ID Command                      | 73   |

| Divisor Latch MSB and LSB Registers    |             | READ TRACK Command                   | 73   |

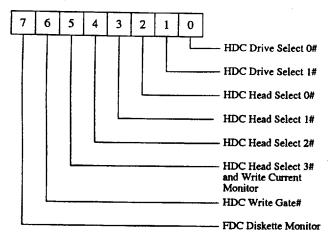

| Hard Disk Controller (HDC) Registers   | 43          | RECALIBRATE Command                  | 74   |

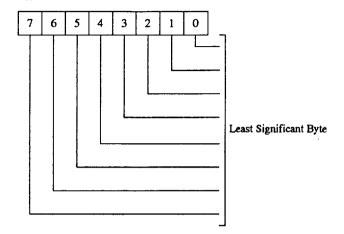

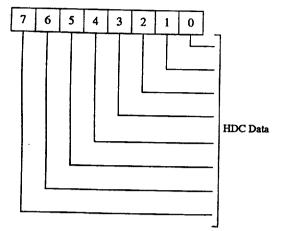

| Data Register                          |             | RELATIVE SEEK Command                | 74   |

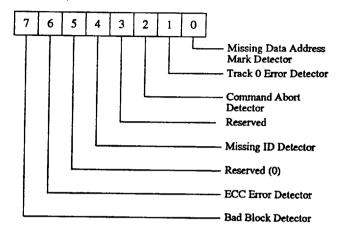

| Error Register                         |             | SCAN EQUAL Command                   | 75   |

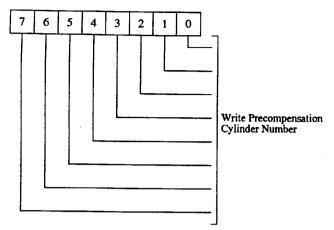

| Write Compensation Register            |             | SCAN HIGH OR EQUAL Command           | 75   |

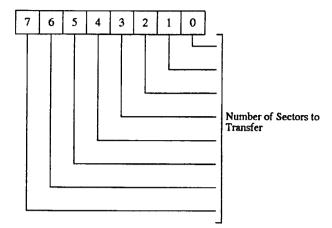

| Sector Count Register                  |             | SCAN LOW OR EQUAL Command            | 76   |

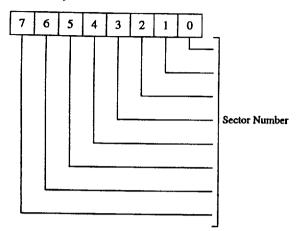

| Sector Number Register                 | 45          | SEEK Command                         | 76   |

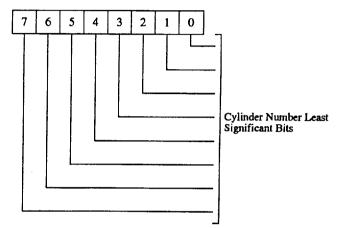

| Low Cylinder Number Register           | 40          | SENSE DRIVE STATUS Command           | 77   |

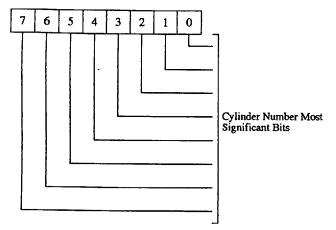

| High Cylinder Number Register          | 40          | SENSE INTERRUPT STATUS Command       | 77   |

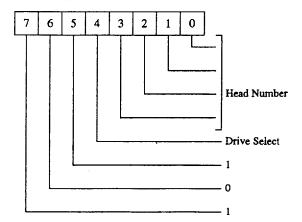

| Drive Select/Head Number Register      | 47          | SPECIFY Command                      |      |

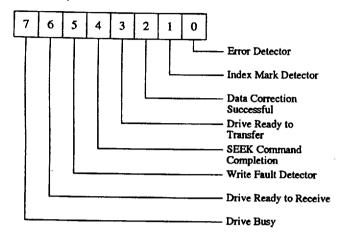

| Status Register                        |             | VERIFY Command                       |      |

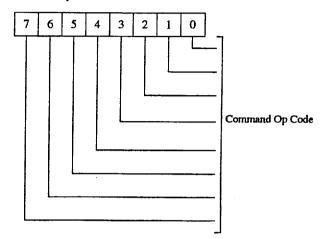

| Command Register                       |             | VERSION Command                      | 79   |

| Alternate Status Register              |             | WRITE DATA Command                   |      |

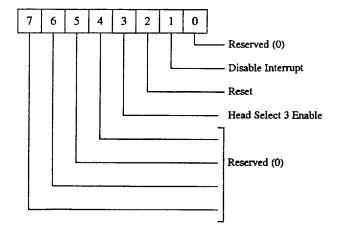

| Fixed Disk Control Register            |             | WRITE DELETED DATA Command           |      |

| Digital Input Register                 |             | Data Transfer Command Descriptions   | 80   |

|                                        |             | READ DATA Command                    |      |

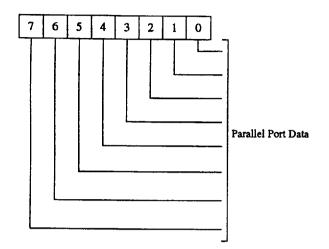

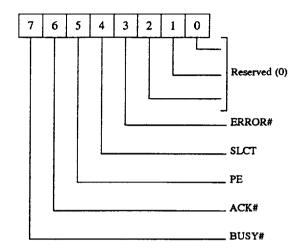

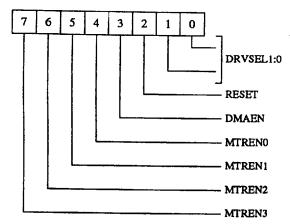

| Parallel Port Registers                | 51          | READ DELETED DATA Command            |      |

| Data Register                          | 52          | READ TRACK Command                   |      |

| Status Register                        |             | WRITE DATA Command                   |      |

| Control Register                       | 53          | WRITE DELETED DATA Command           | 83   |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |             |                                      |      |

| Section                                      | <u>Page</u> | <u>Section</u>                | Page |

|----------------------------------------------|-------------|-------------------------------|------|

| VERIFY Command                               | 83          | Powerdown Mode                | 94   |

| FORMAT TRACK Command                         | 84          | Integrated Circuity           |      |

| Control Command Descriptions                 | 86          | Drive Interface               |      |

| READ ID Command                              | 86          | Parallel Port Interface       |      |

| RECALIBRATE Command                          | 86          | Operation In Standard Mode    |      |

| SEEK Command                                 | 86          | Operation In Bi-Di Mode       |      |

| SENSE INTERRUPT STATUS Command.              | 86          | Power Management Circuitry    |      |

| SENSE DRIVE STATUS Command                   | 87          | Active Mode                   | 05   |

| SPECIFY Command                              | 87          | Sleep Mode                    | 05   |

| CONFIGURE Command                            | 88          | Powerdown Mode                | 05   |

| VERSION Command                              | 88          |                               |      |

| RELATIVE SEEK Command                        | 88          | Electrical Specifications     | 97   |

| DUMPREG Command                              | 89          | Absolute Maximum Ratings      | 07   |

| PERPENDICULAR MODE Command                   | 89          | Capacitance                   | 07   |

| SCAN Commands                                | 90          | DC Electrical Characteristics | 08   |

|                                              |             | AC Timing                     |      |

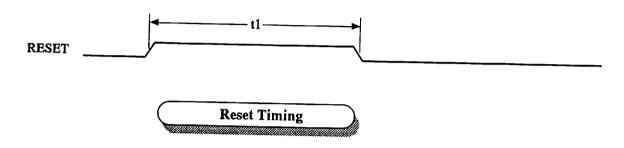

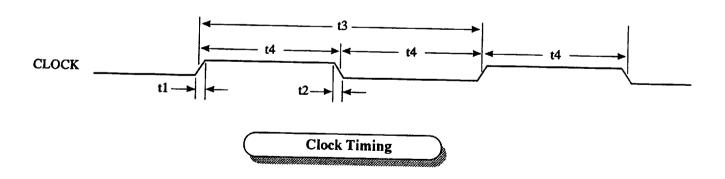

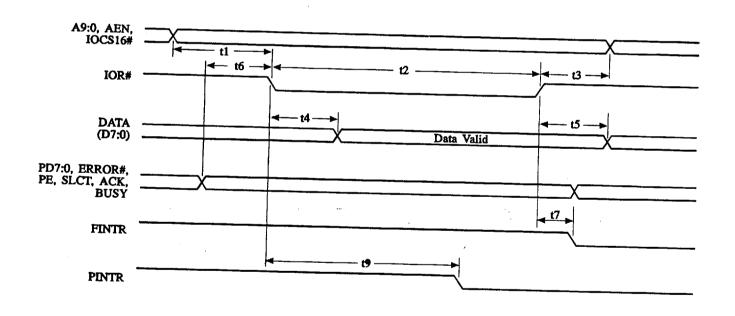

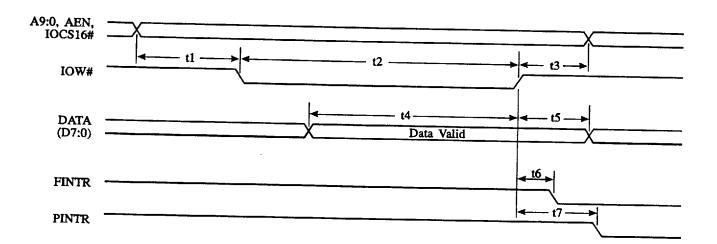

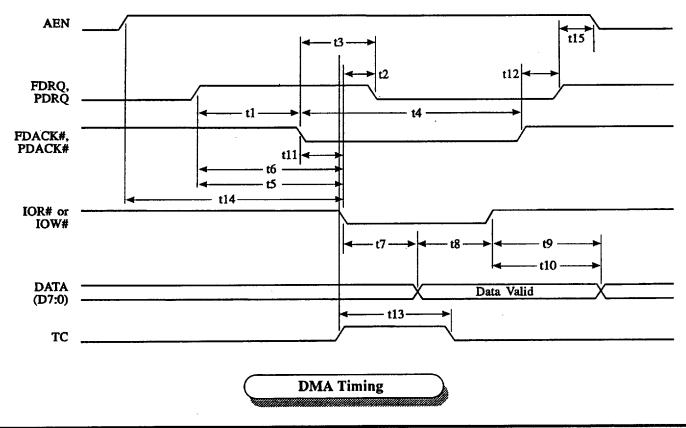

| Functional Description                       | 91          | Reset Timing                  |      |

| Serial Port (UART)                           | 91          | Clock Timing                  |      |

| FIFO Interrupt Mode Operation                | 92          | Microprocessor Read Timing    | 100  |

| FIFO Polled Operation.                       | 92          | Microprocessor Write Timing   | 101  |

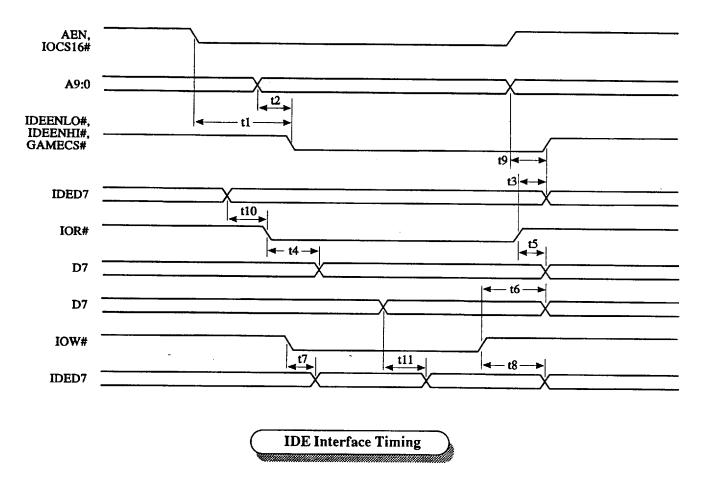

| Integrated Drive Electronics Interface (IDE) | 93          | DMA Timing                    | 102  |

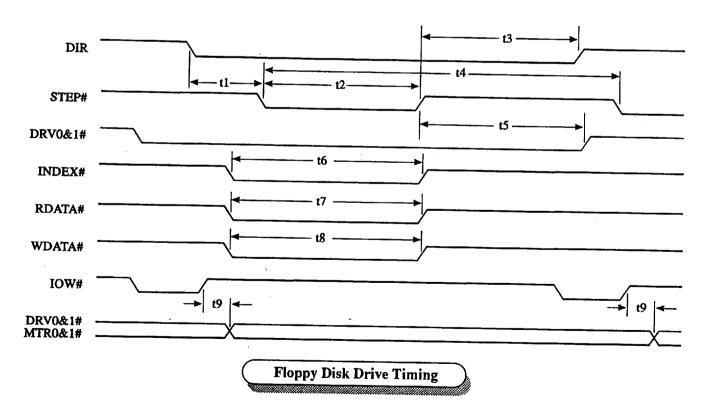

| AT Mode                                      | 93          | Floppy Disk Drive Timing      | 103  |

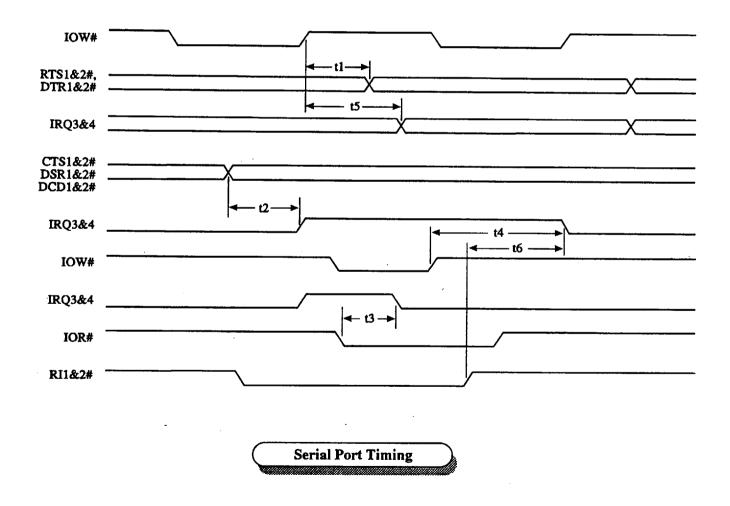

| _ XT Mode                                    | 93          | Serial Port Timing            | 104  |

| Floppy Disk Controller                       | 93          | IDE Interface Timing          | 105  |

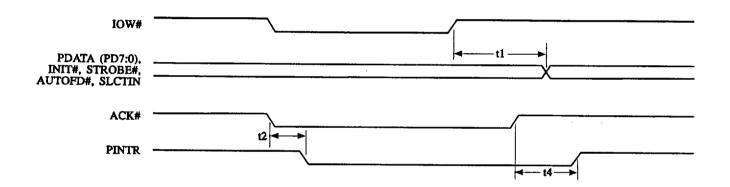

| Precompensation Circuitry                    | 93          | Parallel Port Timing          | 106  |

| Perpendicular Recording Support              | 93          |                               |      |

| Digital Data Separator                       | 94          | Mechanical Specifications     | 107  |

# **List of Figures**

| <u>Figure</u>                 | Page | Figure                                    | Page |

|-------------------------------|------|-------------------------------------------|------|

| System Block Diagram          | 1    | Microprocessor Read Timing                |      |

| Pinout Diagram (100-Pin PQFP) | 9    | Microprocessor Write Timing               | 101  |

| Floppy Disk Formats Supported |      | DMA Timing Floppy Disk Drive Timing       | 102  |

| 82C733 System Organization    |      | Serial Port Timing                        | 104  |

| AC Timing Diagrams            | 99   | IDE Interface Timing Parallel Port Timing | 105  |

| Reset Timing                  | 99   |                                           |      |

| Clock Timing                  | 99   | Mechanical Specifications                 | 107  |

# List of Tables

| <u>Table</u>                                                                                        | <u>Page</u>       | <u>Table</u>                                                                                            | Page     |

|-----------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------|----------|

| Pin List                                                                                            | 10                | Effect of Skip Bit on                                                                                   |          |

| Pin Descriptions                                                                                    |                   | READ DÂTA Command                                                                                       | 81       |

| Register Summary                                                                                    |                   | READ DELETED DATA Result Phase Effect of Skip Bit on                                                    | 82       |

| Configuration Registers Summary Oscillator Enable/Disable Functions COM3, COM4 Address Select       | 23<br>24          | READ DELETEDDATACommand                                                                                 | 83       |

| Interrupt Enable Register Control Function<br>RCVR FIFO Trigger Levels                              | ns 33<br>33<br>36 | Diskette MediaSENSE INTERRUPT STATUS CodesSPECIFY Command Drive Control Delays Effects of WG and GAP on | 87       |

| LCR BITS 0 and 1 EncodingUART Reset Configuration Divisors Baud Rates and Clock Frequenci           | 36<br>37          | PERPENDICULAR MODE Command SN and SH Bit Values for Scan Conditions                                     | 90       |

| Hard Disk Controller Register Summary Parallel Port Register Summary                                | 43                | DC Electrical Characteristics                                                                           | 97       |

| Floppy Drive Control Registers Summary FDC Drive Enable Values                                      | 55                | Absolute Maximum Ratings Capacitance DC Electrical Characteristics                                      | 97       |

| Tape Select Functions  Data Rate Select Encoding  Precompensation Delay Values  Default DelayValues | 57<br>58<br>58    | AC Timing                                                                                               | 99<br>99 |

| Examples of FIFO Service Delay                                                                      | 60                | Microprocessor Read Timing Microprocessor Write Timing                                                  | 101      |

| FDC Command Parameters  Sector Sizes, Read Data Mode  Maximum Data Handling per                     | 67<br>81          | DMA Timing Floppy Disk Drive Timing Serial Port Timing                                                  | 102      |

| READ DATA Command                                                                                   | 81                | IDE Interface Timing                                                                                    | 105      |

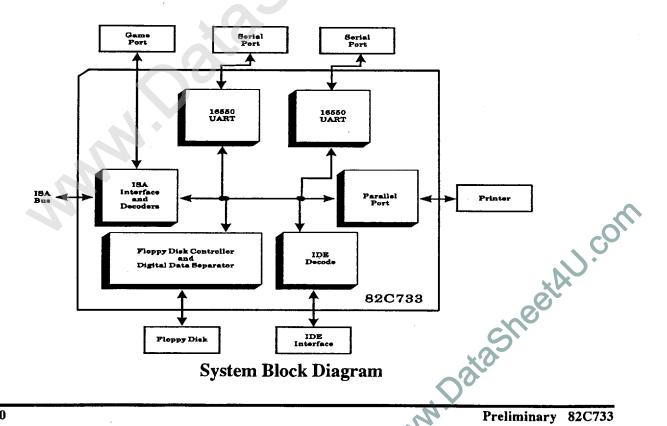

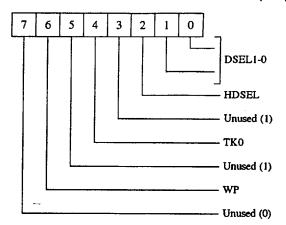

# Introduction

The CHIPS® 82C733 Universal Peripheral Controller is a single-chip solution offering complete I/O capabilities for PC/AT and PC/XT motherboard applications. The controller is configured via software. The 82C733 is a pin compatible with the 82C735 without enhanced parallel port features(Printgine).

The 82C733 features a floppy disk controller, a digital data separator, two 16550 compatible UARTs, an enhanced bidirectional parallel port interface called Printgine, IDE interface control logic, and a game port chip select. For more information about these systems, see the "Functional Description."

# **4MB FLOPPY DISK CONTROLLER**

The floppy disk controller is software compatible with 765B and 82077 controller functions. It provides a 4MB perpendicular recording format as well as the standard floppy drive format for 5.25-inch and 3.5-inch media. The controller supports two drives directly and up to four drives with an external decoder.

### DIGITAL DATA SEPARATOR

The digital data separator is capable of data transfer rates up to 1MB/sec and requires no external components.

#### **NS16550 UARTS AND IDE**

The two licensed NS16550 UARTs are improved versions of the NS16450 UARTs. They are provided with individual 16-byte FIFOs to relieve the CPU of excessive software overhead and are still capable of running existing 16450 software.

The IDE control logic provides a complete IDE interface for embedded hard disk drives.

### PARALLEL PORT INTERFACE

The bidirectional parallel port maintains complete compatibility with ISA and PS/2 modes. It can be configured for either output mode or bidirectional mode.

# **POWER MANAGEMENT**

The 82C733 is provided with several power management features that are controllable through hardware or software. In hardware, the device can be completely powered down through a powerdown pin. In this mode, all inputs are disabled, all outputs are inactive, and the contents of all registers are preserved (as long as the power supply is maintained). In software, the device allows each port to be powered down independently.

Revision 1.0 7 Preliminary 82C733

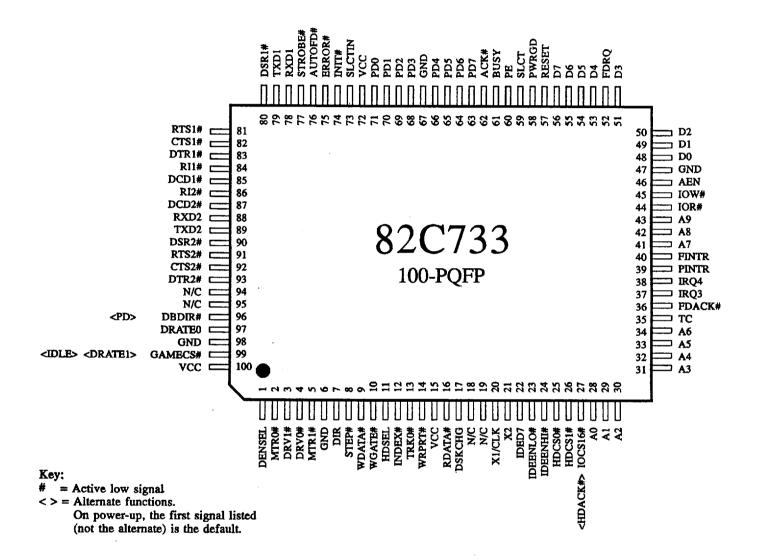

# **Pinout Diagram**

# Pin List

| Pin Name                 | Pin No.    | Dir.           | Buffer      | Driver        |

|--------------------------|------------|----------------|-------------|---------------|

| A0                       | 28         | I              | I           |               |

| A1                       | 29         | I              | I           |               |

| A2                       | 30         | I              | I           | _             |

| A3                       | 31         | ī              | Ī           |               |

| A4                       | 32         | I              | I           |               |

| A.5                      | 33         | I              | I           |               |

| A6                       | 34         | I              | I           |               |

| A7                       | 41         | I              | I           |               |

| A8                       | 42         | I              | Ī           | _             |

| A9                       | 43         | Ī              | I           |               |

| A10                      | 18         | I              | I           |               |

| ACK#                     | 62         | I              | I**         |               |

| AEN                      | 46         | I              | I           |               |

| AUTOFD#                  | 76         | 0              | oc          | 24mA          |

| BUSY                     | 61         | I              | I**         |               |

| CTS1#                    | 82         | I              | ī           |               |

| TS2#                     | 92         | 1              | ī           |               |

| D0                       | 48         | I/O            | I/OH        | 24mA          |

| D1                       | 49         | I/O            | I/OH        | 24mA          |

| D2                       | 50         | 1/0            | I/OH        | 24mA          |

| D3                       | 51         | I/O            | I/OH        | 24mA          |

| 04                       | 53         | I/O            | I/OH        | 24mA          |

| D5                       | 54         | 1/0            | I/OH        | 24mA          |

| D6                       | 55         | I/O            | I/OH        | 24mA          |

| 07                       | 56         | I/O            | I/OH        | 24mA          |

| OBDIR# <pd></pd>         | 96         | O              | 0           | 4mA           |

| DCD1#                    | 85         | I              | I           |               |

| DCD2#                    | 87         | I              | I           |               |

| DENSEL                   | 1          | 0              | OD          | 48mA          |

| DIR                      | 7          | 0              | OD          | 48mA          |

| DRATEO                   | 97         | 0              | 0           | 4mA           |

| DRV0#                    | 4          | 0              | OD          | 48mA          |

| DRV1#                    | 3          | ō              | OD          | 48mA          |

| OSKCHG                   | 17         | I              | IS          |               |

| OSR1#                    | 80         | Ī              | 1           |               |

| OSR2#                    | 90         | I              | Ī           |               |

| OTR1#                    | 83         | ō              | 0           | 4mA           |

| TR2#                     | 93         | ō              | oc          | 16mA          |

| RROR#                    | 75         | <u> </u>       | I**         |               |

| DACK#                    | 36         | Ī              | ī           | <del></del> - |

| DRQ                      | 52         | 0              | Ť           | 24mA          |

| INTR                     | 40         | <del>- 0</del> | T           | 24mA          |

| AMECS#                   | 99         | ō              | ö           | 4mA           |

| DRATEI> <idle></idle>    |            | ŏ              | ŏ           | 4mA           |

| ND                       | 6, 47, 67, |                |             |               |

|                          | 98         |                |             |               |

| IDCS0#                   | 25         | <u> </u>       | 0           | 4mA           |

| DCS1#                    | 26         | 0              | OH          | 24mA          |

| DSEL                     | 11         | <u> </u>       | OD          | 48mA          |

| DED7                     | 22         | 1/0            | <b>І/ОН</b> | 24mA          |

| DEENHI#                  | 24         | 0              | o           | 4mA           |

| DEENLO#                  | 23         | 0              | 0           | 4mA           |

| VDEX#                    | 12         | 1              | IS          |               |

| NIT#                     | 74         | 0              | OC          | 24mA          |

| OCS16# <hdack#></hdack#> | 27         | I              | I           |               |

| OR#                      | 44         | I              | l           |               |

| OW#                      | 45         | I              | I           |               |

| RQ3                      | 37         | 0              | T           | 24mA          |

|                          |            |                |             |               |

| Pin Name | Pin No.           | Dir. | Buffer | Driver |

|----------|-------------------|------|--------|--------|

| IRQ4     | 38                | 0    | T      | 24mA   |

| MTRO#    | 2                 | 0    | OD     | 48mA   |

| MTRI#    | 5                 | 0    | OD     | 48mA   |

| N/C      | 18, 19,<br>94, 95 |      |        |        |

| PD0      | 71                | 1/0  | ОН     | 24mA   |

| PD1      | 70                | I/O  | OH     | 24mA   |

| PD2      | 69                | I/O  | OH     | 24mA   |

| PD3      | 68                | I/O  | OH     | 24mA   |

| PD4      | 66                | I/O  | ОН     | 24mA   |

| PD5      | 65                | I/O  | OH     | 24mA   |

| PD6      | 64                | 1/0  | OH     | 24mA   |

| PD7      | 63                | Í/O  | ОН     | 24mA   |

| PDACK#   | 19                | I    | I**    | ·      |

| PDRQ     | 94                | 0    | T      | 24mA   |

| PINTR    | 39                | 0    | T      | 24mA   |

| PE       | 60                | I    | I**    |        |

| PWRGD    | 58                | I    | I      |        |

| RDATA#   | 16                | I    | IS     |        |

| RESET    | 57                | I    | IS     |        |

| RI1#     | 84                | I    | I      |        |

| RI2#     | 86                | I    | I      |        |

| RTS1#    | 81                | 0    | 0      | 4mA    |

| RTS2#    | 91                | 0    | 0      | 4mA    |

| RXD1     | 78                | 1    | I      | _      |

| RXD2     | 88                | I    | I      |        |

| SLCT     | 59                | I    | I**    |        |

| SLCTIN#  | 73                | 0    | OC     | 24mA   |

| STEP#    | 8                 | 0    | OD     | 48mA   |

| STROBE#  | 77                | 0    | OC     | 24mA   |

| rc       | 35                | I    | I      |        |

| TRK0#    | 13                | I    | IS     |        |

| TXD1     | 79                | 0    | 0      | 4mA    |

| TXD2     | 89                | 0    | OC     | 16mA   |

| Vcc      | 15, 72,<br>100    |      |        |        |

| WDATA#   | 9                 | Out  | OD     | 48mA   |

| WGATE#   | 10                | Out  | OD     | 48mA   |

| WRPRT#   | 14                | In   | IS     |        |

| XI/CLK   | 20                | In   | Iclk   |        |

| X2       | 21                | Out  | 0      | 4mA    |

Revision 1.0

Notes:

I - TTL input; Iclk - clock input; IS - Schmitt-trigger input;

O - TTL output (4mA); OC- open-drain output (16mA or 24mA);

OD - high-current open-drain output (48mA); OH - high-current TTL output (24mA); T- tristate TTL output (24mA);

\*\* - pin has internal pull-up resistor.

# **Pin Descriptions**

# PIN DESCRIPTIONS

**Host Interface**

| Pin<br>Number   | Pin<br>Name  | Туре   | Active<br>Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|--------------|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43-41,<br>34-28 | A9-A0        | I      | High            | Host I/O Address Bus. Pins A9-0 are latched internally at the beginning of IOR# or IOW#.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 56-53,<br>51-48 | D7-0         | I/O    | High            | Host Bidirectional Data Bus. The data bus transfers information between the CPU and the 82C733.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

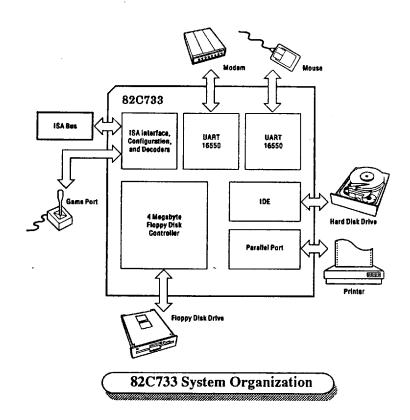

| 57              | RESET        | I      | High            | Master Reset. This Schmitt-trigger input from the host resets serial ports, parallel port, integrated drive electronics (IDE), and floppy drive controller (FDC). Configuration registers are not affected.                                                                                                                                                                                                                                                                                                                                          |

| 44              | IOR#         | I      | Low             | I/O Read. IOR# is an active low input from the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 45              | IOW#         | I      | Low             | I/O Write. IOW# is an active low input from the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 46              | AEN          | I      | Low             | Address Enable. AEN indicates DMA activity. It is normally used with the address bus and IOW#/IOR# to decode I/O address ports.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 37<br>38        | IRQ3<br>IRQ4 | T<br>T | High<br>High    | Serial Port Interrupt Request (programmable Polarity). These interrupts are associated with the serial ports. IRQ4 initiates the signal if the serial channel has been designed as COM1 or COM3. IRQ3 initiates the signal if the channel is COM2 or COM4. The appropriate interrupt is enabled/disabled via the Interrupt Enable Register (IER). The interrupt is reset inactive after the appropriate interrupt service routine is executed, after it is disabled via the IER, or after a RESET. For more information see "Serial Port Registers." |

| 39              | PINTR        | 0      | High            | Printer Port Interrupt Request (programmable polarity). This signal is generated following the ACK# signal input.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 52              | FDRQ         | 0      | High            | Floppy Controller DMA Request. If DMA is not used, this pin is tristated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 36              | FDACK#       | I      | Low             | Floppy Controller DMA Acknowledge. This pin is normally used to enable DMA read or write.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 40              | FINTR        | 0      | High            | Floppy Controller Interrupt Request (programmable polarity). FINTR is used to get the CPU's attention. The required action depends on the current function of the controller.                                                                                                                                                                                                                                                                                                                                                                        |

| 35              | TC           | 1      | High            | <b>Terminal Count.</b> This input indicates termination of DMA transfer. The signal is qualified by DACK# before it is used on the chip.                                                                                                                                                                                                                                                                                                                                                                                                             |

**Primary Serial Port**

| Pin<br>Number | Pin<br>Name | Туре | Active<br>Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|-------------|------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 82            | CTS1#       | I    | Low             | Clear to Send (primary). When low, CTS1# indicates that the modem or data set is ready to exchange data. The CPU can monitor this signal's status by reading bit 4 of the modem status register (MSR) of the primary serial port. MSR<4> is the complement of CTS#. MSR<0> shows whether the signal has changed state since the previous MSR reading. If bit 3 of the Interrupt Enable Register (IER) is set, the interrupt is generated when CTS# changes state. This signal has no effect on the transmitter. For additional register information, see "Serial Port Registers." |

| 80            | DSR1#       | I    | Low             | Data Set Ready (primary). When low, DSR1# indicates that the modem or data set is ready to establish a communications link. The CPU can monitor the signal's status by reading bit 5 of the Modem Status Register (MSR) of the primary serial port. MSR<5> is the complement of DSR#. MSR<1> indicates whether the signal has changed state since the previous MSR reading. If bit 3 of the Interrupt Enable Register (IER) is set, the interrupt is generated when signal DSR# changes state. See "Serial Port Registers" for more register information.                         |

| 85            | DCD1#       | I    | Low             | Data Carrier Detect (primary). When low, DCD1# indicates that the modem or data set has detected the data carrier. The CPU can monitor the status of DCD1# by reading bit 7 of the Modem Status Register (MSR) primary serial port. MSR<7> is the complement of DCD#. MSR<3> indicates whether the signal has changed state since the previous MSR reading. If bit 3 of the Interrupt Enable Register (IER) is set, the interrupt is generated when DCD# changes state. For additional register information, see "Serial Port Registers."                                         |

| 84            | RI1#        | I    | Low             | Ring Indicator (primary). When low, RI1# indicates that the modem has received a telephone ringing signal. The CPU can monitor the status of RI1# by reading bit 6 of the Modem Status Register (MSR) of the primary serial port. MSR<6> is the complement of RI#. MSR<2> indicates whether the signal has changed state since the previous MSR reading. If bit 3 of the Interrupt Enable Register (IER) is set, the interrupt is generated when RI# changes state. See "Serial Port Registers" for more register information.                                                    |

| 78            | RXD1        | I    | Low             | Serial Input (primary). This signal receives serial data input from the communications link.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 81            | RTS1#       | 0    |                 | Request to Send (primary). When low, RTS1# indicates to the modem or data set that the UART is ready to exchange data. This signal can be set to an active low by programming bit 1 of the Modem Control Register (MCR) to a high level (see "Serial Port Registers"). A hardware reset sets the signal to its inactive (high) state; a loop mode operation holds it in its inactive state.                                                                                                                                                                                       |

| 83            | DTR1#       | 0    |                 | Data Terminal Ready (primary). When low, DTR1# indicates that the modem or data set is ready to establish a communications link. This signal can be set to an active low by programming bit 0 of the Modem Control Register (MCR) to a high level (see "Serial Port Registers"). A hardware reset sets this signal to its inactive (high) state; a loop mode operation holds it in its inactive state.                                                                                                                                                                            |

| 79            | TXD1        | 0    |                 | Serial Output (primary). TXD1 sends serial output to the communications link. This signal is set to a marking (logic 1) state on a hardware reset, when the transmitter is empty, or when a loop mode operation is initiated.                                                                                                                                                                                                                                                                                                                                                     |

Secondary Serial Port

| Pin<br>Number | Pin<br>Name | Туре | Active<br>Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|-------------|------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 92            | CTS2#       | I    | Low             | Clear to Send (secondary). When low, this input indicates that the modem or data set is ready to exchange data. The CPU can monitor this signal's status by reading bit 4 of the Modem Status Register (MSR) of the secondary serial port. MSR<4> is the complement of CTS#. MSR<0> shows whether the signal has changed state since the previous MSR reading. If bit 3 of the Interrupt Enable Register (IER) is set, the interrupt is generated when CTS# changes state. This signal has no effect on the transmitter. For more register information, see "Serial Port Registers." |

| 90            | DSR2#       | I    | Low             | Data Set Read (secondary). When low, DSR2# indicates that the modem or data set is ready to establish a communications link. The CPU can monitor this signal's status by reading bit 5 of the Modem Status Register (MSR) of the secondary serial port. MSR<5> is the complement of DSR#. MSR<1> indicates whether this input has changed state since the previous MSR reading. If bit 3 of the Interrupt Enable Register (IER) is set, the interrupt is generated when signal DSR# changes state. For additional register information, see "Serial Port Registers."                 |

| 87            | DCD2#       | I    | Low             | Data Carrier Detect (secondary). When low, DCD2# indicates that the modem or data set has detected the data carrier. The CPU can monitor the status of this signal by reading bit 7 of the Modem Status Register (MSR) secondary serial port. MSR<7> is the complement of DCD#. MSR<3> indicates whether this input has changed state since the previous MSR reading. If bit 3 of the Interrupt Enable Register (IER) is set, the interrupt is generated when DCD# changes state. For additional register information, see "Serial Port Registers."                                  |

| 86            | RI2#        | I    | Low             | Ring Indicator (secondary). When low, RI2# indicates that the modem has received a telephone ringing signal. The CPU can monitor the status of RI2# by reading bit 6 of the Modem Status Register (MSR) of the secondary serial port. MSR<6> is the complement of RI#. MSR<2> indicates whether the signal has changed state since the previous MSR reading. If bit 3 of the Interrupt Enable Register (IER) is set, the interrupt is generated when RI# changes state. See "Serial Port Registers" for additional register information.                                             |

| 88            | RXD2        | I    | High            | Serial Input (secondary). This signal receives serial data input from the communications link.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 91            | RTS2#       | 0    | Low             | Request to Send (secondary). When low, RTS2# indicates to the modem or data set that the UART is ready to exchange data. RTS2# can be set to an active low by programming bit 1 of the Modem Control Register (MCR) to a high level (see "Serial Port Registers"). A hardware reset sets this signal to its inactive (high) state; a loop mode operation holds it in its inactive state.                                                                                                                                                                                             |

| 93            | DTR2#       | 0    | Low             | Data Terminal Ready (secondary). When low, DTR2# indicates that the modem or data set is ready to establish a communications link. This signal can be set to an active low by programming bit 0 of the Modem Control Register (MCR) to a high level (see "Serial Port Registers"). A hardware reset sets this signal to its inactive (high) state; a loop mode operation holds it in its inactive state.                                                                                                                                                                             |

| 89            | TXD2        | . 0  | High            | Serial Output (secondary). TXD2 sends serial output to the communications link. This signal is set to the marking (logic 1) state on a hardware reset, when the transmitter is empty, or when a loop mode operation is initiated.                                                                                                                                                                                                                                                                                                                                                    |

IDE Interface

| Pin<br>Number | Pin<br>Name       | Туре | Active<br>Level | Description                                                                                                                                                                                                                                                                                                                                           |

|---------------|-------------------|------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27            | IOCS16#           | I    | Low             | I/O Chip Select 16-Bit. This pin is driven by the peripheral device when it can accommodate a 16-bit access. The hard disk interface generates IOCS16# to inform the host and the 82C733 that 16-bit I/O transfers are about to begin. This signal is active only when data is being transferred in AT mode.                                          |

|               | <hdack#></hdack#> | I    | Low             | Hard Disk Acknowledge (alternate). This input is used to acknowledge the DMA request in the XT hard disk mode.                                                                                                                                                                                                                                        |

| 25            | HDCS0#            | 0    | Low             | Hard Disk Chip Select 0 for IDE Interface. In AT mode, this signal decodes addresss space 1F0H-1F7H if the primary address is used, or space 170H-177H if the secondary address is used. In XT mode, HDCS0# decodes address space 320H-323H. This pin is inactive if IDE is disabled via the configuration registers (see "Configuration Registers"). |

| 26            | HDCS1#            | 0    | Low             | Hard Disk Chip Select 1 for IDE Interface. In AT mode, HDCS1# decodes addresss space 3F6H-3F7H if the primary address is used, or space 376H-377H if the secondary address is used. This pin is inactive in XT mode and when IDE is disabled via the configuration registers (see "Configuration Registers").                                         |

| 22            | IDED7             | I/O  | High            | IDE Data Bit 7. This pin provides the data bus bit 7 signal to the IDE hard drive during accesses to addresses 1F0H-1F7H, 170H-177H, 3F6H, and 376H. The pin is tristated during read or write accesses to 3F7H and 377H. In the XT hard disk mode, IDED7 is not used.                                                                                |

| 24            | IDEENHI#          | Ο    | Low             | IDE High Data Buffer Enable. This output enables the high byte data latch during a read or write to the hard disk. The pin is active only when IOCS16# is active and AT mode is selected. It is not used in XT mode and is also inactive when the IDE is disabled.                                                                                    |

| 23            | IDEENLO#          | 0    | Low             | IDE Low Data Buffer Enable. This output enables the low byte data latch during a read or write to the hard disk. It is valid in both AT and XT modes.                                                                                                                                                                                                 |

# **Parallel Port**

| Pin<br>Number   | Pin<br>Name | Туре | Active<br>Level | Description                                                                                                                                                                                                                |

|-----------------|-------------|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63-66,<br>68-71 | PD7-PD0     | I/O  | High            | Parallel Port Data Bus. This bidirectional parallel data bus is used to transfer information between the CPU and peripherals. PD7-0 are configured as open drain pins in standard Centronics and PS/2 bidirectional modes. |

| 77              | STROBE#     | 0    | Low             | Data Strobe. This output indicates to the peripheral device that the data at the parallel port is valid. A pull-up resistor should be provided for this pin.                                                               |

| 61              | BUSY        | I    | High            | Busy. This input indicates that the printer cannot accept more data. The pin has an internal pull-up resistor attached to it.                                                                                              |

| 62              | ACK#        | I    | Low             | Acknowledge. This input is pulsed by the peripheral device to indicate that it has received the data and is ready to accept more data. The pin has an internal pull-up resistor attached to it                             |

| 76              | AUTOFD#     | 0    | Low             | Automatic Feed. This active low output causes the printer to add a line feed after each line is printed. The pin should be provided with a pull-up resistor                                                                |

| 73              | SLCTIN#     | 0    | Low             | Select Input. This active low output selects the printer. A pull-up resistor should be provided on this pin.                                                                                                               |

| 74              | INIT#       | 0    | Low             | Initialize. This active low output initializes (resets) the printer. A pull-up resistor should be provided on this pin.                                                                                                    |

| 59              | SLCT        | I    | High            | Select. The printer sets this input high when it is selected. SLCT has an internal pull-up resistor attached to it.                                                                                                        |

| 75              | ERROR#      | I    | Low             | Error. The printer sets this input low when it detects an error. The pin has an internal pull-up resistor attached to it.                                                                                                  |

| 60              | PE          | I    | High            | Paper End. This input indicates that the printer is out of paper. The pin has an internal pull-up resistor attached to it                                                                                                  |

| 96              | DBDIR#      | 0    | Low             | Host Data Bus Buffer Direction. This active low signal indicates read cycles for 82C733 internal accesses.                                                                                                                 |

|                 | <pd></pd>   | 0    | High            | <b>Power Down (alternate).</b> This signal goes high when the floppy disk controller is in powerdownmode.                                                                                                                  |

Floppy Controller

| Pin<br>Number | Pin<br>Name    | Туре | Active<br>Level | 2 4541 iption                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|----------------|------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

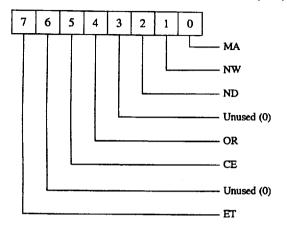

| 16            | RDATA#         | I    | Low             | Read Data. This Schmitt-trigger input reads raw data from the disk.                                                                                                                                                                                                                                                                                                                                                                                               |

| 9             | WDATA#         | 0    | Low             | Write Data. This output writes precompensated serial data to the selected drive and is gated internally with WGATE#. Precompensation is software selectable.                                                                                                                                                                                                                                                                                                      |

| 10            | WGATE#         | 0    | Low             | Write Gate. This output signal enables the head of the selected disk drive to write to the disk.                                                                                                                                                                                                                                                                                                                                                                  |

| 4 3           | DRV0#<br>DRV1# | 0    | Low<br>Low      | Drive Select 0 and 1. These signals are decoded drive select outputs for drives 0 and 1, respectively. They are controlled by bits D0 and D1 of the Digital Ouput Register (see "Floppy Drive Control (FDC) Registers"). Two drives can be supported directly when the 2-drive option is selected via bit 3 of CR05H (see "Configuration Registers"). When the 4-drive option is selected, these pins are encoded with information to control four floppy drives. |

| 2 5           | MTR0#<br>MTR1# | 0    | Low<br>Low      | Motor Select 0 and 1. These are motor enable outputs for drives 0 and 1, respectively. They are controlled by bits D4-D7 of the Digital Output Register (see "Floppy Drive Control (FDC) Registers"). Two drives can be supported directly when the 2-drive option is selected via bit 3 of CR05H (see "Configuration Registers"). When the 4-drive option is selected, these pins are encoded with information to control four floppy drives.                    |

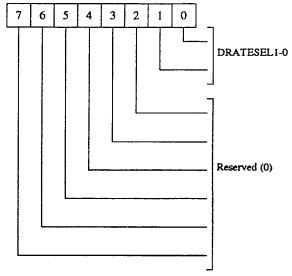

| 97            | DRATE0         | 0    | High            | Data Rate 0. This totem-pole buffered output reflects the currently selected FDC data rate (bit 0 of the Configuration Control Register or the Data Rate Register, whichever was written to last). For additional register information, see "Floppy Drive Control (FDC) Registers."                                                                                                                                                                               |

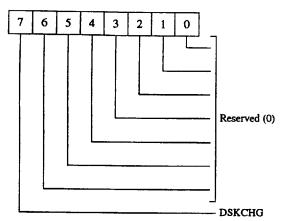

| 17            | DSKCHG         | I    | High            | Diskette Change. This Schmitt-trigger input notifies the floppy drive controller that the disk drive door has been opened. The state of this pin is available from the Digital Input Register (see "Floppy Drive Control (FDC) Registers").                                                                                                                                                                                                                       |

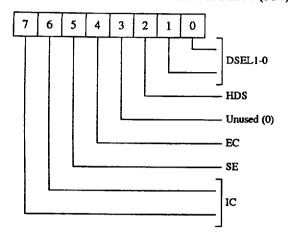

| 1             | DENSEL         | 0    | High            | Density Select. This output indicates whether a low data rate (250/300Kbps) or a high data rate (500Kbps/1Mbps) has been selected.                                                                                                                                                                                                                                                                                                                                |

| 7             | DIR            | 0    | High            | Direction. This output signal controls the direction of the floppy disk drive head movement during a seek operation (low - step in; high - step out).                                                                                                                                                                                                                                                                                                             |

| 8             | STEP#          | 0    | Low             | Step. This output signal supplies step pulses, at a software programmable rate, to move the head during a seek operation.                                                                                                                                                                                                                                                                                                                                         |

| 11            | HDSEL          | 0    | High            | <b>Head Select.</b> This output determines the side of the floppy disk being accessed (low - side 0; high - side 1).                                                                                                                                                                                                                                                                                                                                              |

| 13            | TRKO#          | I    | Low             | Track 0. This Schmitt-trigger input indicates that the head of the selected floppy drive is on track zero.                                                                                                                                                                                                                                                                                                                                                        |

| 14            | WRPRT#         | I    | Low             | Write Protect. This Schmitt-trigger input indicates that the disk in the selected drive is write-protected.                                                                                                                                                                                                                                                                                                                                                       |

| 12            | INDEX          | I    | High            | Index. This Schmitt-trigger input indicates the beginning of a track.                                                                                                                                                                                                                                                                                                                                                                                             |

# Clock and Miscellaneous

| Pin<br>Number     | Pin<br>Name       | Type | Active<br>Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|-------------------|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20                | X1/CLK            | I    | High            | Crystal 1/Clock. This pin is an external connection for a resonant 24MHz crystal. A TTL or CMOS compatible oscillator is connected to this pin if a crystal is not used.                                                                                                                                                                                                                                                                                                                                                                             |

| 21                | X2                | O    | High            | Crystal 2. This pin is the second connection for a 24MHz crystal. If an external clock is used, the pin is left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 58                | PWRGD             | I    | High            | Power Good. This input signal indicates that power (VCC) is valid. For the device to be operational, the signal must be active high. The 82C733 is fully functional when PWRGD is active.  When Vcc is valid and PWRGD is inactive, the 82C733 is isolated from the rest of the circuit: all accesses are ignored, all inputs are disabled, and all outputs are tristated. However, the contents of all registers are preserved, and the current drain drops to standby current (Istby).  An internal weak pull-up resistor is attached to this pin. |

| 99                | GAMECS#           | 0    | Low             | Game Port Chip Select. This pin is low when I/O address 201H is selected. The function of this pin is determined by bits 2 and 1 of CR05H (see "Configuration Registers").                                                                                                                                                                                                                                                                                                                                                                           |

|                   | <drate1></drate1> | Ο    | High            | Data Rate 1 (alternate). This totem-pole buffered output reflects the current floppy drive controller data rate (bit 1 of the Configuration Control Register or the Data Rate Register, whichever was written to last). For additional register information, see "Floppy Drive Control (FDC) Registers."                                                                                                                                                                                                                                             |

|                   | <idle></idle>     | 0    | High            | Idle (alternate). This pin goes high when the floppy drive Idle state is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18, 19,<br>94, 95 | N/C               |      |                 | No Connects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15, 72<br>100     | VCC               |      |                 | +5VDC digital power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6, 47<br>67, 98   | GND               |      | -               | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# **Register Summary**

| Register             | Register Group       | Register Name                   | Bits             | Access | Port (Hex)   | Alt<br>Port  | Alt<br>Port | Alt<br>Port  | Index |

|----------------------|----------------------|---------------------------------|------------------|--------|--------------|--------------|-------------|--------------|-------|

| CR00                 | Configuration        | FDC / HDC Configuration         | 7                | R/W    | 3F0-3F1h     | -            | _           | _            | 00    |

| CR01                 | Configuration        | Serial / Parallel Configuration | 8                | R/W    | 3F0-3F1h     |              | _           | _            | 01    |

| CR02                 | Configuration        | Serial Pri / Sec Configuration  | 8                | R/W    | 3F0-3F1h     | -            | _           | _            | 02    |

| CR03                 | Configuration        | Serial Port Test Mode           | 4                | R/W    | 3F0-3F1h     | _            | -           | _            | 03    |

| CR04                 | Configuration        | Serial Port 2 Configuration     | 1                | R/W    | 3F0-3F1h     | <del>-</del> | -           | _            | 04    |

| CR05                 | Configuration        | FDC Configuration               | 8                | R/W    | 3F0-3F1h     |              | -           | _            | 05    |

| CR06                 | Configuration        | FDC Configuration               | 1                | R/W    | 3F0-3F1h     |              | _           | <del>-</del> | 06    |

| DOR                  | FDC                  | Digital Output                  | 8<br>8<br>7<br>8 | R/W    | 3F2          | 372          | _           |              | n/a   |

| MSR                  | FDC                  | Main Status                     | 8                | R      | 3F4          | 374          | -           | -            | n/a   |

| DSR                  | FDC                  | Data Rate Select                | 7                | W      | 3F4          | 374          | -           |              | n/a   |

| FIFO                 | FDC                  | Data (FIFO)                     | 8                | R/W    | 3F5          | 375          | _           | <del>-</del> | n/a   |

| DIR                  | FDC                  | Digital Input                   | 1                | R      | 3F7          | 377          | -           | _            | n/a   |

| CCR                  | FDC                  | Configuration Control           | 1<br>2           | W      | 3F7          | 377          | -           |              | n/a   |

| HDATA                | HDC                  | Data                            | 8                | R/W    | 1F0          | 170          | _           |              | n/a   |

| HWCMP                | HDC                  | Write Precomp                   | 8                | W      | 1 <b>F</b> 1 | 171          | _           | _            | n/a   |

| HERR                 | HDC                  | Егтог                           | 6                | R      | 1 <b>F</b> 1 | 171          | -           | _            | n/a   |

| HSC                  | HDC                  | Sector Count                    |                  | R<br>W | 1F2          | 172          | _           | _            | n/a   |

| HSN                  | HDC                  | Sector Number                   | 8<br>8           | R/W    | 1F3          | 173          | _           | <del>-</del> | n/a   |

| HCL                  | HDC                  | Low Cylinder                    | 8                | R/W    | 1F4          | 174          | <u> </u>    | <del>-</del> | n/a   |

| НСН                  | HDC                  | High Cylinder                   | 8                | R/W    | 1 <b>F</b> 5 | 175          | _           | _            | n/a   |

| HDH                  | HDC                  | Drive Select / Head #           | 8                | R/W    | 1F6          | 176          | _           | -            | n/a   |

| HCMD                 | HDC                  | Command                         | 8                | W      | 1F7          | 177          | <u> </u>    | _            | n/a   |

| HSTAT                | HDC                  | Status                          | 8                | R      | 1F7          | 177          | <u> </u>    | _            | n/a   |

| HSTAT2               | HDC                  | Alternate Status                | 8                | R      | 3F6          | 376          | <u> </u>    | _            | n/a   |

| HCTRL                | HDC                  | Fixed Disk Control              | 3                | W      | 3F7          | 377          | _           | -            | n/a   |

| HIN                  | HDC                  | Digital Input                   | 3<br>8           | W<br>R | 3F7          | 377          | _           | _            | n/a   |

| DATA                 | Parallel             | Data                            | 8                | R/W    | 278          | 378          | 3BC         | -            | n/a   |

| DSR                  | Parallel             | Status                          | 6                | R      | 279          | 379          | 3BD         | _            | n/a   |

| DCR                  | Parallel             | Control                         | 6                | R/W    | 27A          | 37A          | 3BE         | _            | π/a   |

| DLL                  | Serial (1 of 2 sets) | Divisor Latch LSB (DLAB=1)      | 8                | R/W    | Base+0       |              | -           | _            | n/a   |

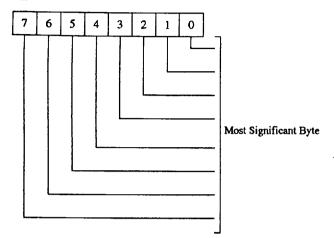

| DLM                  | Serial (1 of 2 sets) | Divisor Latch MSB (DLAB=1)      | 8                | R/W    | Base+1       | _            | ÷ –         | _            | n/a   |

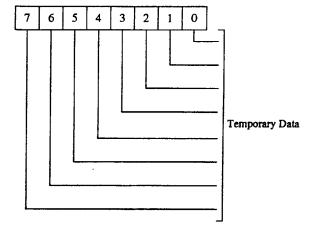

| RBR                  | Serial (1 of 2 sets) | Rcv Buffer Reg (DLAB=0)         | 8                | R      | Base+0       | -            | _           | _            | n/a   |

| THR                  | Serial (1 of 2 sets) | Xmt Holding Reg (DLAB=0)        | 8                | W      | Base+0       | _            | -           |              | n/a   |

| IER                  | Serial (1 of 2 sets) | Interrupt Enable (DLAB=0)       | 4                | R/W    | Base+1       | <u> </u>     | <u> </u>    | _            | n/a   |

| ΠR                   | Serial (1 of 2 sets) | Interrupt ID                    | 6                | R      | Base+2       | _            | _           |              | n/a   |

| FCR                  | Serial (1 of 2 sets) | FIFO Control                    | 6                | W      | Base+2       | _            | _           | -            | n/a   |

| LCR                  | Serial (1 of 2 sets) | Line Control                    | 8                | R/W    | Base+3       | _            | · –         | : <u> </u>   | n/a   |

| MCR                  | Serial (1 of 2 sets) | Modern Control                  | 5                | R/W    | Base+4       | -            | _           | <u> </u>     | n/a   |

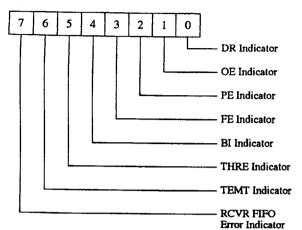

| LSR                  | Serial (1 of 2 sets) | Line Status                     | 8                | R/W    | Base+5       | -            | _           | _            | n/a   |

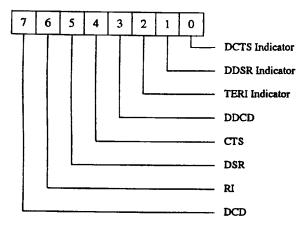

| MSR                  | Serial (1 of 2 sets) | Modem Status                    | 8                | R/W    | Base+6       |              | _           | <u> </u>     | n/a   |

| SCR                  | Serial (1 of 2 sets) | Scratchpad                      | 8                | R/W    | Base+7       | _            | _           | _            | n/a   |

| COM1BASE             | COM1 Base Address    |                                 |                  | Base:  | 3F8          | _            | _           | _            | n/a   |

| COM1BASE<br>COM2BASE | COM1 Base Address    |                                 | •                | Base:  | 2F8          | <u> </u>     | · -         |              | n/a   |

| COM2BASE             | COM2 Base Address    | <u> </u>                        |                  | Base:  | 338          | 3E8          | 2E8         | 220          | n/a   |

| COM3BASE<br>COM4BASE | COM4 Base Address    |                                 | †                | Base:  | 238          | 2E8          | 2E0         | 228          | n/a   |

# **Registers**

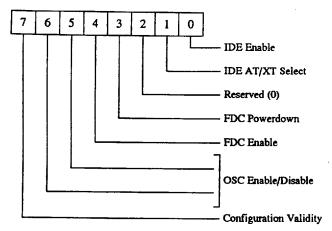

# **CONFIGURATION REGISTERS**

The seven read/write configuration registers are configurable by software. Two consecutive I/O addresses, one even and one odd, are used to select and access the registers (see "Configuration Procedures"under "Configuration Registers"). These addresses should not conflict with any other devices. By IBM PC convention, the address range 3F0H to 3F7H is reserved for the floppy disk controller (FDC). In the 82C733, address range 3F0H to 3F1H can be used for configuring the system.

The configuration registers do not have to be initialized if the default values are used for normal operation. The registers are set to the default state only upon power-up and are not affected by the RESET signal. Settings are retained as long as power to the chip is maintained.

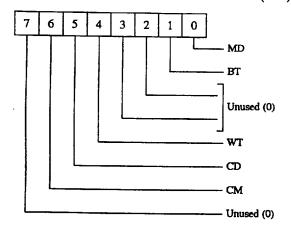

#### **SERIAL PORT REGISTERS**

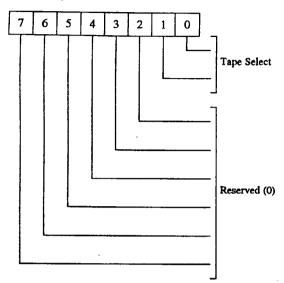

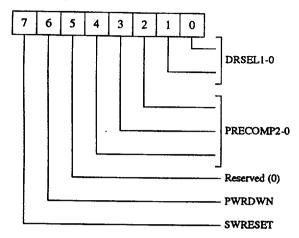

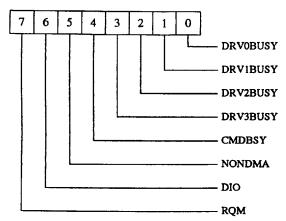

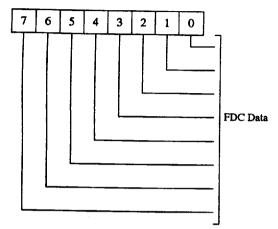

The 82C733 provides two identical serial port (UART) register sets, one for each channel. The register descriptions provided in the section "Serial Port Registers" apply to both sets of UART registers.